Ffotosynhwyrydd un-ffotonwedi torri trwy'r tagfa effeithlonrwydd o 80%

Ffoton senglffotosynhwyryddyn cael eu defnyddio'n helaeth ym meysydd ffotonig cwantwm a delweddu un-ffoton oherwydd eu manteision cryno a chost isel, ond maent yn wynebu'r tagfeydd technegol canlynol.

Cyfyngiadau technegol cyfredol

1.CMOS a SPAD cyffordd denau: Er bod ganddyn nhw integreiddio uchel a jitter amseru isel, mae'r haen amsugno yn denau (ychydig ficrometrau), ac mae'r PDE yn gyfyngedig yn y rhanbarth agos-is-goch, gyda dim ond tua 32% ar 850 nm.

2. SPAD cyffordd drwchus: Mae'n cynnwys haen amsugno degau o ficrometrau o drwch. Mae gan gynhyrchion masnachol PDE o tua 70% ar 780 nm, ond mae torri trwy 80% yn hynod heriol.

3. Darllen cyfyngiadau'r gylched: Mae angen foltedd gor-duedd o dros 30V ar SPAD cyffordd drwchus i sicrhau tebygolrwydd uchel o eirlithriad. Hyd yn oed gyda foltedd diffodd o 68V mewn cylchedau traddodiadol, dim ond i 75.1% y gellir cynyddu'r PDE.

Datrysiad

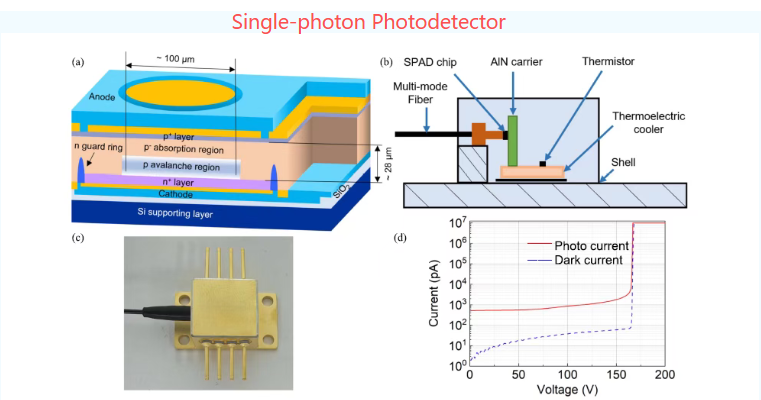

Optimeiddio strwythur lled-ddargludyddion SPAD. Dyluniad wedi'i oleuo'n ôl: Mae ffotonau digwyddiadol yn dadfeilio'n esbonyddol mewn silicon. Mae'r strwythur wedi'i oleuo'n ôl yn sicrhau bod mwyafrif y ffotonau'n cael eu hamsugno yn yr haen amsugno, a bod yr electronau a gynhyrchir yn cael eu chwistrellu i'r rhanbarth eirlithriad. Gan fod cyfradd ïoneiddio electronau mewn silicon yn uwch na chyfradd tyllau, mae chwistrelliad electronau yn darparu tebygolrwydd uwch o eirlithriad. Rhanbarth eirlithriad iawndal dopio: Trwy ddefnyddio'r broses drylediad barhaus o boron a ffosfforws, mae'r dopio bas yn cael ei iawndal i ganolbwyntio'r maes trydan yn y rhanbarth dwfn gyda llai o ddiffygion crisial, gan leihau sŵn fel DCR yn effeithiol.

2. Cylchdaith darlleniad perfformiad uchel. Diffodd osgled uchel 50V Pontio cyflwr cyflym; Gweithrediad amlfodd: Trwy gyfuno signalau DIFFODDI ac AILOSOD rheolaeth FPGA, cyflawnir newid hyblyg rhwng gweithrediad rhydd (sbardun signal), giatio (gyriant GATE allanol), a moddau hybrid.

3. Paratoi a phecynnu dyfeisiau. Mabwysiadir y broses waffer SPAD, gyda phecyn pili-pala. Mae'r SPAD wedi'i fondio i'r swbstrad cludwr AlN ac wedi'i osod yn fertigol ar yr oerydd thermoelectrig (TEC), a chyflawnir rheolaeth tymheredd trwy thermistor. Mae ffibrau optegol amlfodd wedi'u halinio'n fanwl gywir â chanolfan y SPAD i gyflawni cyplu effeithlon.

4. Calibradu perfformiad. Cynhaliwyd y calibradu gan ddefnyddio deuod laser pwls picosecond 785 nm (100 kHz) a thrawsnewidydd amser-digidol (TDC, datrysiad 10 ps).

Crynodeb

Drwy optimeiddio strwythur SPAD (cyffordd drwchus, wedi'i oleuo'n ôl, iawndal dopio) ac arloesi'r gylched diffodd 50 V, llwyddodd yr astudiaeth hon i wthio PDE y synhwyrydd un-ffoton sy'n seiliedig ar silicon i uchder newydd o 84.4%. O'i gymharu â chynhyrchion masnachol, mae ei berfformiad cynhwysfawr wedi'i wella'n sylweddol, gan ddarparu atebion ymarferol ar gyfer cymwysiadau fel cyfathrebu cwantwm, cyfrifiadura cwantwm, a delweddu sensitifrwydd uchel sy'n gofyn am effeithlonrwydd uwch-uchel a gweithrediad hyblyg. Mae'r gwaith hwn wedi gosod sylfaen gadarn ar gyfer datblygiad pellach synhwyrydd sy'n seiliedig ar silicon.synhwyrydd un-ffotontechnoleg.

Amser postio: Hydref-28-2025